Advanced Micro Devices said that its next-generation Epyc server chip module, code-named Rome, will have 64 cores based on the Zen 2 architecture. It will also have twice the performance per central processing unit socket as the previous generation, and it will have four times the floating point performance per socket.

Rome will consist of eight chips, with eight cores per die, all glued together in a multichip module with accompanying input-output functions — in a single socket.

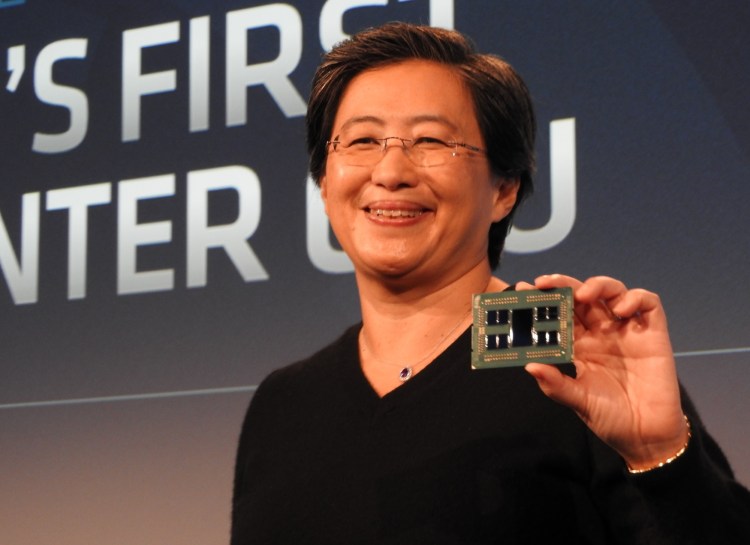

Lisa Su, CEO of AMD, said that the new chip module will debut next year with a 7-nanometer manufacturing process (where the circuits are seven billionths of a meter wide). Rome will have eight 7-nanometer cores per die (or chip), plus a 14-nanometer input/output die.

“It is the best datacenter processor in the industry,” said Su, speaking onstage at the AMD press and analyst day in San Francisco. “We are absolutely on track to debut Rome in 2019. This is our space. This is where we lead.”

June 5th: The AI Audit in NYC

Join us next week in NYC to engage with top executive leaders, delving into strategies for auditing AI models to ensure fairness, optimal performance, and ethical compliance across diverse organizations. Secure your attendance for this exclusive invite-only event.

The input-output chip will be made with a 14-nanometer manufacturing process. Su and AMD senior vice president Forrest Norrod showed a demo of Rome executing a benchmark. It completed the test in 28 seconds, in comparison to 30 seconds for an Intel two-socket solution with the Intel Xeon Scalable 8180M. That’s a pretty impressive result, said Bob O’Donnell, analyst at TECHnalysis Research.

The Rome module will have Zen 2 cores, which are based on the second-generation architecture of the Zen platform that AMD introduced in the spring of 2017. Those Zen chips could execute 52 percent more instructions per clock cycle than the previous generation, and Su said that the Rome chips will beat that measure.

Zen 2 chips are sampling today at 7-nanometer manufacturing, compared to the shipping 14-nanometer Zen processors that debuted in 2017. Zen 3 is on track to debut on 7-nanometer in 2020. AMD is using TSMC, the chip contract manufacturer, to make its 7-nanometer chips. Intel, meanwhile, has delayed its equivalent chips, dubbed 10-nanometer but at the same technology level, until late 2019.

Zen 2 can get twice the throughput thanks to better branch prediction, or predicting what kind of processing will be necessary for the next computation. It also has better 256-bit load/store floating point processing, or double the previous generation.

Zen 2 will also have stronger built-in security, where data can be fully encrypted as it is transferred to memory.

Norrod said that Epyc adoption can lead to 45 percent lower total cost of ownership (TCO) compared to Intel-based systems. He said that comes as a result of lower admin, licensing, hardware, and space costs.

Pete Ungaro, CEO of Cray, said onstage that his company’s upcoming Shasta supercomputer will use AMD Epyc processors. The machine will be made for government agencies such as the Lawrence Berkeley National Laboratory and will run at 100 petaflops.

Patrick Moorhead, analyst at Moor Insights & Strategy, said he thinks the large multichip modules are the future of entire chip industry. AMD called the chip components within this package “chiplets.”

As for Rome, he said, “AMD is showing yet again its commitment to a very aggressive product improvement roadmap. With Rome, AMD is changing everything. It is changing its system-on-chip architecture to 7-nanometer ‘chiplets with an improved Infinity Fabric, doubling cores per socket, doubling bandwidth per socket, adding PCIe 4.0 and improving core and FPU capabilities.”

He added, “AMD says this will deliver an impressive 2X performance per socket and 4X on floating point unit (FPU) per socket. With all these improvements, AMD made Rome “socket-compatible” with Naples, which should accelerate uptake with [computer makers] and ultimately, end customers. As AMD has delivered on its promises the last two years, I have little doubt AMD will deliver on-time, at quality.”